- 您现在的位置:买卖IC网 > Sheet目录1904 > ATF1502ASV-15JI44 (Atmel)IC CPLD EE HP 15NS 44-PLCC

2

1615J–PLD–01/06

ATF1502ASV

1.

Description

The ATF1502ASV is a high-performance, high-density complex programmable logic device

(CPLD) that utilizes Atmel’s proven electrically-erasable technology. With 32 logic macrocells

and up to 36 inputs, it easily integrates logic from several TTL, SSI, MSI, LSI and classic PLDs.

The ATF1502ASV’s enhanced routing switch matrices increase usable gate count and the odds

of successful pin-locked design modifications.

The ATF1502ASV has up to 32 bi-directional I/O pins and four dedicated input pins, depending

on the type of device package selected. Each dedicated pin can also serve as a global control

signal, register clock, register reset or output enable. Each of these control signals can be

selected for use individually within each macrocell.

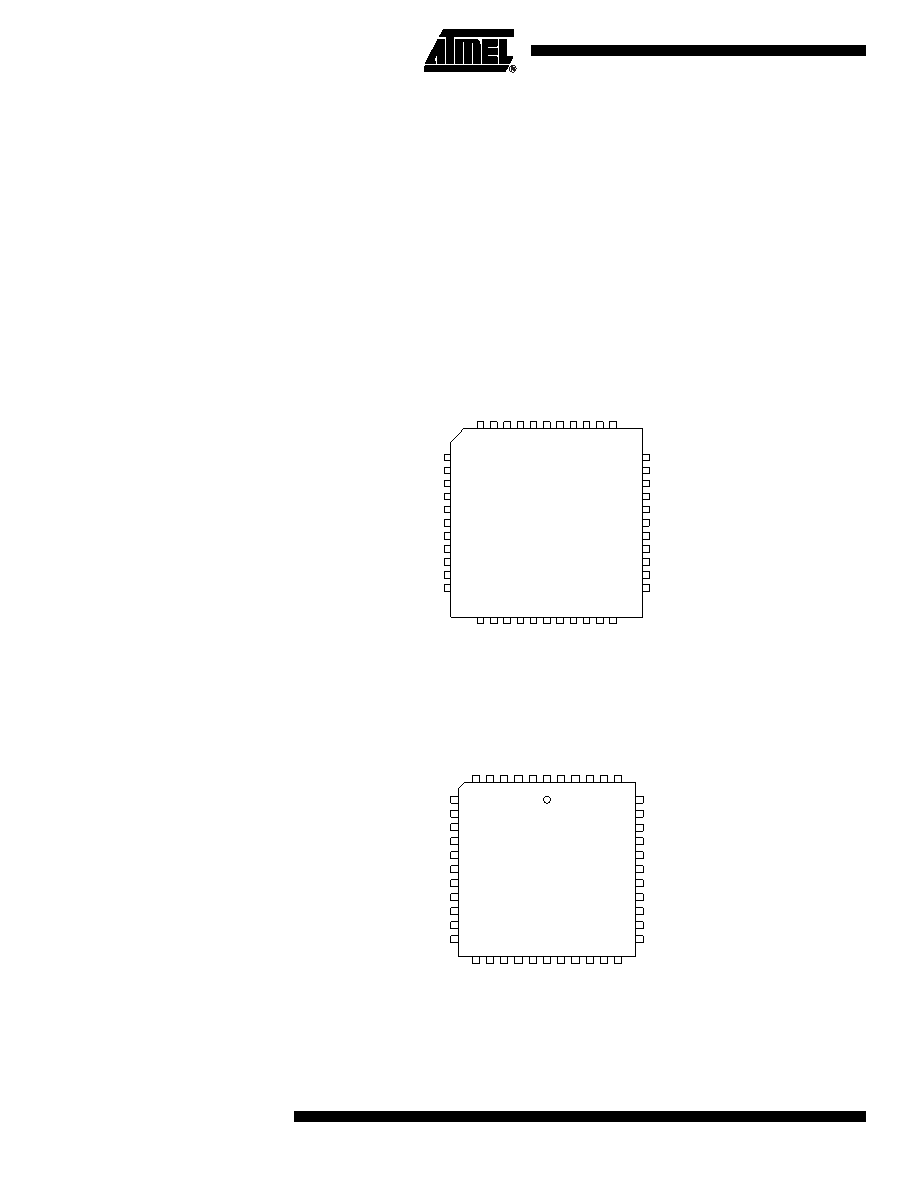

Figure 1-1.

44-lead TQFP Top View

Figure 1-2.

44-lead PLCC Top View

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

I/O/TDI

I/O

GND

PD1/I/O

I/O

TMS/I/O

I/O

VCC

I/O

I/O/TDO

I/O

VCC

I/O

I/O/TCK

I/O

GND

I/O

44

43

42

41

40

39

38

37

36

35

34

12

13

14

15

16

17

18

19

20

21

22

I/O

GND

VCC

I/O

PD2/I/O

I/O

VCC

GCLK2/OE2/I

GCLR/I

I/OE1

GCLK1/I

GND

GCLK3/I/O

I/O

7

8

9

10

11

12

13

14

15

16

17

39

38

37

36

35

34

33

32

31

30

29

TDI/I/O

I/O

GND

PD1/I/O

I/O

I/O/TMS

I/O

VCC

I/O

I/O/TDO

I/O

VCC

I/O

I/O/TCK

I/O

GND

I/O

6

5

4

3

2

1

44

43

42

41

40

18

19

20

21

22

23

24

25

26

27

28

I/O

GND

VCC

I/O

PD2/I/O

I/O

VCC

GCLK2/OE2/I

GCLR/I

OE1/I

GCLK1/I

GND

GCLK3/I/O

I/O

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ATF1502BE-5AX44

IC CPLD 64MC 1.8V 44-TQFP

ATF1504ASVL-20QI100

IC CPLD 20NS LOWV LOWPWR 100QPFP

ATF1504BE-5AX100

IC CPLD 64MC 1.8V 100-TQFP

ATF1508ASL-25QI160

IC CPLD 25NS LOW PWR 160PQFP

ATF1508ASVL-20JU84

IC CPLD 20NS LOWV LOW PWR 84PLCC

ATF1508BE-5AX100

IC CPLD 128MC 1.8V ISP 100TQFP

ATF1508RE-5AX100

IC CPLD 128MC 3.3V ISP 100TQFP

ATF1508RE-7AU100

IC CPLD EE 128MC 5NS 100-TQFP

相关代理商/技术参数

ATF1502ASV-15JU44

功能描述:CPLD - 复杂可编程逻辑器件 CPLD 32 MACROCELL ISP STD PWR 3.3V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100

ATF1502ASV-20AC44

功能描述:CPLD - 复杂可编程逻辑器件 CPLD 32 MACROCELL ISP STD PWR 3.3V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100

ATF1502ASV-20AI44

功能描述:CPLD - 复杂可编程逻辑器件 CPLD 32 MACROCELL ISP STD PWR 3.3V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100

ATF1502ASV-20JC44

功能描述:CPLD - 复杂可编程逻辑器件 ASICS RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100

ATF1502ASV-20JI44

功能描述:CPLD - 复杂可编程逻辑器件 ASICS RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100

ATF1502ASVL-30AC44

功能描述:IC CPLD 32 MC 30NS EE 44TQFP 制造商:microchip technology 系列:ATF15xx 包装:托盘 零件状态:停產 可编程类型:系统内可编程(最少 10,000 次编程/擦除循环) 延迟时间 tpd(1)最大值:30.0ns 电源电压 - 内部:3 V ~ 3.6 V 宏单元数:32 I/O 数:32 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:44-TQFP 供应商器件封装:44-TQFP(10x10) 基本零件编号:ATF1502 标准包装:154

ATF1502ASVL-30JC44

功能描述:IC CPLD 32 MC 30NS EE 44PLCC 制造商:microchip technology 系列:ATF15xx 包装:托盘 零件状态:停產 可编程类型:系统内可编程(最少 10,000 次编程/擦除循环) 延迟时间 tpd(1)最大值:30.0ns 电源电压 - 内部:3 V ~ 3.6 V 宏单元数:32 I/O 数:32 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:44-LCC(J 形引线) 供应商器件封装:44-PLCC(16.59x16.59) 基本零件编号:ATF1502 标准包装:27

ATF1502BE

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Highperformance CPLD